FPGA并行時(shí)序驅(qū)動布局算法

大小:1.14 MB 人氣: 2018-02-26 需要積分:1

推薦 + 挑錯(cuò) + 收藏(0) + 用戶評論(0)

標(biāo)簽:FPGA(595779)時(shí)序(37047)

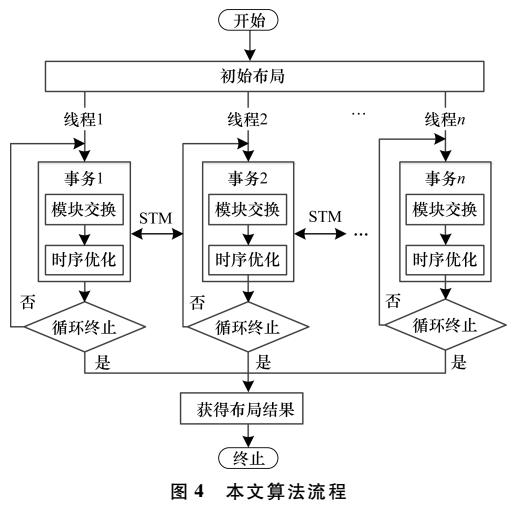

傳統(tǒng)的基于模擬退火的現(xiàn)場可編程門陣列( FPGA)時(shí)序驅(qū)動布局算法在時(shí)延代價(jià)的計(jì)算上存在一定誤差,已有的時(shí)序優(yōu)化算法能夠改善布局質(zhì)量,但增加了時(shí)耗。針對上述問題,提出一種基于事務(wù)內(nèi)存( TM)的并行FPGA時(shí)序布局算法TM—DCP。將退火過程分發(fā)至多線程執(zhí)行,利用TM機(jī)制保證共享內(nèi)存訪問的合法性,并將改進(jìn)的時(shí)序優(yōu)化算法嵌入到事務(wù)中并發(fā)執(zhí)行。測試結(jié)果表明,與通用布局布線工具相比,8線程下的TM—DCP算法在總線長僅有輕微增加的情況下,關(guān)鍵路徑時(shí)延平均降低了4.2%,同時(shí)獲得了1.7倍的加速,且其執(zhí)行速度隨線程數(shù)的增加具有較好的可擴(kuò)展性。

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

下載地址

FPGA并行時(shí)序驅(qū)動布局算法下載

相關(guān)電子資料下載

- 怎么建設(shè)Xilinx FPGA Artix-A7教學(xué)實(shí)驗(yàn)室?山西工學(xué)院給您答案 122

- 5G通信大贏家?除了FPGA外,AMD 5G射頻產(chǎn)品讓人眼前一亮 1167

- 中科億海微FPGA+ARM核心板在自動噴漆設(shè)備中的應(yīng)用 47

- 中科億海微SoM模組——國產(chǎn)風(fēng)扇控制板 70

- 中科億海微成功入選2023“科創(chuàng)中國”先導(dǎo)技術(shù)榜 131

- 一文了解FPGA技術(shù)知識 927

- 基于安路科技FPSoC器件DR1系列的視頻采集/顯示/處理解決方案 504

- 萊迪思半導(dǎo)體推出全新MachXO5D-NX FPGA和Sentry解決方案 313

- 芒果樹FPGA光纖通訊卡支持萬兆UDP,可傳輸至PC手機(jī)等設(shè)備 32

- 萊迪思推出全新安全控制FPGA系列產(chǎn)品 331