從制造的角度來講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA、然后是測(cè)試FPGA,配置FPGA是指將FPGA通過將配

2011-10-12 15:16:25 1414

1414

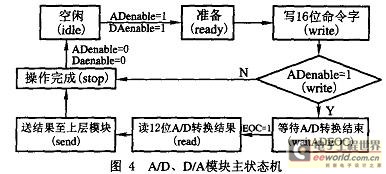

本文研究了一種電容在線測(cè)試方法,并以向FPGA內(nèi)植入Nios II軟核作為控制器,以控制信號(hào)源的發(fā)生與測(cè)試檔位的自動(dòng)切換。實(shí)驗(yàn)證明了該測(cè)試方法的可行性及較高的精準(zhǔn)度,達(dá)到了設(shè)計(jì)目的。

2015-02-03 10:52:34 1222

1222

為了方便對(duì)1553B設(shè)備進(jìn)行測(cè)試,介紹了一種基于ARM9平臺(tái)和FPGA的1553B總線測(cè)試系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)方法。該系統(tǒng)以LPC3250作為微處理器,以CYCLONE I系列的EP1C6Q240C8芯片實(shí)現(xiàn)ARM與1553B協(xié)議芯片的接口邏輯。

2015-04-21 14:49:08 3666

3666

基于eFPGAsim的電機(jī)硬件在環(huán)測(cè)試系統(tǒng),是面向電驅(qū)HIL測(cè)試的高精度FPGA的解決方案,利用最新的eHS (Electric Hardware Solver)技術(shù)實(shí)現(xiàn),在獲得基于FPGA片上仿真

2017-08-09 10:52:21 2930

2930

利用FPGA可重復(fù)編程的特性,通過脫機(jī)配置,建立BIST邏輯,即使由于線路被操作系統(tǒng)的重新配置而令BIST結(jié)構(gòu)消失,可測(cè)性也可實(shí)現(xiàn)。本文給出一種基于BIST利用ORCA(Optimized

2018-11-28 09:02:00 4021

4021

? ? ? ? ? ? ? ? ?能否通過SerDes的loopback選項(xiàng)實(shí)現(xiàn)上述的測(cè)試方法?

? ? ? ? 3、有更簡(jiǎn)單易行的測(cè)試方法嗎?

2018-06-21 06:25:29

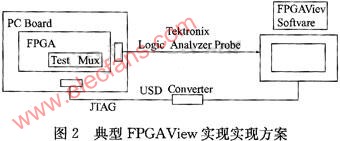

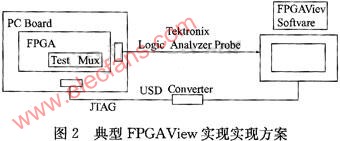

大容量、高速率和低功耗已成為FPGA的發(fā)展重點(diǎn)。嵌入式邏輯分析工具無法滿足通用性要求,外部測(cè)試工具可以把FPGA內(nèi)部信號(hào)與實(shí)際電路聯(lián)合起來觀察系統(tǒng)真實(shí)運(yùn)行情況。隨著FPGA技術(shù)的發(fā)展,大容量、高速

2019-08-07 07:50:15

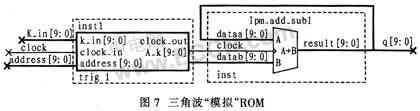

上面介紹的是整個(gè) FPGA 固件系統(tǒng)的實(shí)現(xiàn)方法,為了驗(yàn)證設(shè)計(jì)的正確性,還需要編寫一個(gè)測(cè)試平臺(tái)對(duì)整個(gè)系統(tǒng)進(jìn)行仿真。由于實(shí)際情況下 FPGA 是和 PDIUSBD12 進(jìn)行通信,所以在測(cè)試平臺(tái)中需要虛擬

2018-11-28 15:22:56

FPGA在嵌入式測(cè)試系統(tǒng)中的優(yōu)勢(shì)是什么?FPGA在嵌入式測(cè)試系統(tǒng)中的不足是什么?

2021-05-06 07:19:22

概念上初步實(shí)現(xiàn)了自動(dòng)重復(fù)下載和重復(fù)測(cè)試的功能,為FPGA自動(dòng)化測(cè)試尋找到一個(gè)好方法;(2)利用軟件的靈活性提高了測(cè)試系統(tǒng)中具有可觀察性好和可控制性強(qiáng)的優(yōu)勢(shì);利用硬件結(jié)構(gòu)上并行度高、速度快的優(yōu)勢(shì)提高了測(cè)試的效率;(3)相較于專業(yè)的ATE設(shè)備,該系統(tǒng)軟件可控性更強(qiáng),配置數(shù)據(jù)更方便。

2020-05-14 07:00:00

目前買了一批FPGA的核心板,在使用之前希望能先測(cè)試核心板的好壞,現(xiàn)在的測(cè)試方法是讓核心板的所有引腳輸出不同頻率的方波,然后用示波器看是否有波形輸出。但效果視乎不太理想,有的板子會(huì)有部分引腳無波形

2015-12-11 12:02:09

的性能指標(biāo),設(shè)計(jì)有效的方法來測(cè)試。實(shí)際上入侵檢測(cè)系統(tǒng)的測(cè)試是一個(gè)難度較大的問題,也是一件費(fèi)時(shí)耗力的工作。對(duì)于這一工作,許多研究機(jī)構(gòu)都進(jìn)行了相應(yīng)的研究,給出了自己的測(cè)試方法和測(cè)試結(jié)果。例如MIT的林肯實(shí)驗(yàn)室

2019-08-19 06:55:17

處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點(diǎn)。但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)

2019-07-05 06:21:42

介紹幾種常用的單片機(jī)系統(tǒng)RAM測(cè)試方法,并在原有基礎(chǔ)上提出了一種基于種子和逐位倒轉(zhuǎn)的RAM故障測(cè)試方法。

2021-04-09 06:15:29

FPGA可重復(fù)配置和測(cè)試系統(tǒng)結(jié)構(gòu)概述FPGA重復(fù)配置和測(cè)試的實(shí)現(xiàn)

2021-04-29 06:58:20

有一個(gè)合理的投資回報(bào)(ROI)。本文從解決靈活性、可伸縮和高效測(cè)試等問題入手,介紹既能經(jīng)濟(jì)地滿足今天的要求,又能保護(hù)未來投資的合成測(cè)試系統(tǒng)方法。

2019-06-04 06:11:59

單片機(jī)測(cè)試內(nèi)容及實(shí)現(xiàn)方法單片機(jī)測(cè)試案列分析

2021-03-01 06:00:40

1 RAM測(cè)試方法回顧 (1)方法1 參考文獻(xiàn)中給出了一種測(cè)試系統(tǒng)RAM的方法。該方法是分兩步來檢查,先后向整個(gè)數(shù)據(jù)區(qū)送入#00H和#FFH,再先后讀出進(jìn)行比較,若不一樣,則說明出錯(cuò)。 (2

2011-04-15 09:29:48

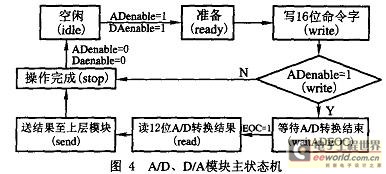

,測(cè)試控制電路比較復(fù)雜,測(cè)試點(diǎn)的查找方法以及切換方法直接影響測(cè)試機(jī)的測(cè)試速度,本文研究了基于FPGA的硬件控制系統(tǒng)設(shè)計(jì)。 硬件控制系統(tǒng) 測(cè)試過程是在上位計(jì)算機(jī)的控制下,控制測(cè)試電路分別打開不同的測(cè)試

2018-08-27 15:54:29

實(shí)物測(cè)試結(jié)果圖。實(shí)測(cè)結(jié)果驗(yàn)證了系統(tǒng)功能實(shí)現(xiàn)的正確性,PC端可循環(huán)發(fā)送命令,FPGA端接收并解析命令進(jìn)行相應(yīng)的控制(開關(guān)切換、信號(hào)采集等),然后將數(shù)據(jù)回饋到PC端,實(shí)現(xiàn)了多通道綜合測(cè)試系統(tǒng)的設(shè)計(jì)。圖 11

2018-08-07 10:08:19

安捷倫公司數(shù)字測(cè)試資深技術(shù)/市場(chǎng)工程師 冀衛(wèi)東為滿足日益復(fù)雜的數(shù)字化系統(tǒng)的設(shè)計(jì)要求,FPGA的密度及復(fù)雜性也在急速增長(zhǎng),越來越多的系統(tǒng)或子系統(tǒng)功能在FPGA內(nèi)部實(shí)現(xiàn),其先進(jìn)的功能和高集成度使FPGA成為極具吸引力的解決方案,進(jìn)而也使得基于內(nèi)核的FPGA測(cè)試方案浮出水面。

2019-07-11 06:15:12

如何實(shí)現(xiàn)自動(dòng)重復(fù)配置和FPGA測(cè)試,將FPGA較快速度的在線配置和快速測(cè)試結(jié)合起來。

2021-04-08 06:14:46

通用測(cè)試系統(tǒng)是如何組成的?如何實(shí)現(xiàn)通用測(cè)試系統(tǒng)的硬件設(shè)計(jì)?如何實(shí)現(xiàn)通用測(cè)試系統(tǒng)的軟件設(shè)計(jì)?

2021-04-14 06:47:55

本文的設(shè)計(jì)是基于FPGA實(shí)現(xiàn)邏輯芯片的功能故障測(cè)試。由于FPGA芯片價(jià)格的不斷下降和低端芯片的不斷出現(xiàn),使用FPGA作為主控芯片可以更適合于市場(chǎng),且有利于對(duì)性能進(jìn)行擴(kuò)展。實(shí)驗(yàn)表明,該系統(tǒng)設(shè)計(jì)合理,能對(duì)被測(cè)芯片進(jìn)行準(zhǔn)確的功能測(cè)試。

2021-04-30 06:13:48

怎么實(shí)現(xiàn)基于FPGA的VRLA蓄電池測(cè)試系統(tǒng)的設(shè)計(jì)?

2021-05-10 06:22:19

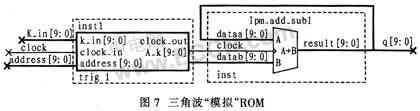

本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測(cè)試系統(tǒng)具有較強(qiáng)的競(jìng)爭(zhēng)力。本系統(tǒng)在FPGA單板單片主控器件控制下,實(shí)現(xiàn)兩路獨(dú)立、幅值可控的信號(hào)發(fā)生器,一路虛擬存儲(chǔ)示波器,具有外部觸發(fā)信號(hào)和采樣時(shí)鐘的16路高速邏輯分析儀。

2021-05-12 06:58:02

燃料開關(guān)測(cè)試系統(tǒng)的組成及工作原理是什么?燃料開關(guān)具有什么功能?怎么實(shí)現(xiàn)燃料開關(guān)測(cè)試系統(tǒng)的設(shè)計(jì)?

2021-05-17 06:21:54

動(dòng)態(tài)測(cè)試技術(shù)是以捕捉和處理各種動(dòng)態(tài)信息為目的的一門綜合技術(shù),它在當(dāng)代科學(xué)技術(shù)中地位十分重要,在航天航空、儀器儀表、交通運(yùn)輸、軍事、醫(yī)療等研究中均應(yīng)用廣泛。常用的測(cè)試方法有遙測(cè)與存儲(chǔ)測(cè)試,與無線電遙測(cè)

2019-08-26 06:44:45

隨著嵌入式系統(tǒng)的發(fā)展,迫切需要在嵌入式系統(tǒng)開發(fā)階段對(duì)嵌入式系統(tǒng)進(jìn)行離線測(cè)試與分析,以保證系統(tǒng)的軟件應(yīng)用程序、硬件具有兼容性、高可靠性和高可用性,迅速發(fā)現(xiàn)并準(zhǔn)確定位系統(tǒng)中存在的問題。本文結(jié)合上海貝爾阿爾卡特股份有限公司開發(fā)的寬帶交換系統(tǒng),討論離線單板硬件測(cè)試方法和系統(tǒng)測(cè)試方法。

2019-07-05 07:24:18

離線單板硬件測(cè)試方法有哪些?嵌入式系統(tǒng)離線測(cè)試方法有哪些?

2021-04-23 07:22:51

基于magnum II測(cè)試系統(tǒng)的測(cè)試技術(shù)研究,提出了采用magnum II測(cè)試系統(tǒng)的APG及其他模塊實(shí)現(xiàn)對(duì)MRAM VDMR8M32進(jìn)行電性測(cè)試及功能測(cè)試。其中功能測(cè)試包括全空間讀寫數(shù)據(jù)0測(cè)試,全空間讀寫

2019-07-23 07:25:23

風(fēng)機(jī)性能測(cè)試系統(tǒng)的設(shè)計(jì)與研究 風(fēng)機(jī)性能測(cè)試系統(tǒng)的設(shè)計(jì)與研究風(fēng)機(jī)性能測(cè)試系統(tǒng)的設(shè)計(jì)與研究風(fēng)機(jī)在植保機(jī)械上的應(yīng)用非常廣泛,風(fēng)機(jī)的性能直接影響到風(fēng)送式植保機(jī)械的射程、藥液霧化性能、霧滴穿透能力及防飄移性能

2021-09-06 08:35:39

風(fēng)機(jī)性能測(cè)試系統(tǒng)的設(shè)計(jì)與研究風(fēng)機(jī)性能測(cè)試系統(tǒng)的設(shè)計(jì)與研究風(fēng)機(jī)性能測(cè)試系統(tǒng)的設(shè)計(jì)與研究風(fēng)機(jī)在植保機(jī)械上的應(yīng)用非常廣泛,風(fēng)機(jī)的性能直接影響到風(fēng)送式植保機(jī)械的射程、藥液霧化性能、霧滴穿透能力及防飄移性能

2021-09-13 08:35:15

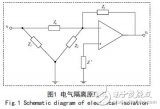

為了克服測(cè)試方法和測(cè)試人員給絕緣耐壓測(cè)試結(jié)果帶來的誤差,提出了一種智能化多路絕緣耐壓自動(dòng)測(cè)試系統(tǒng)的設(shè)計(jì)方法。介紹了該系統(tǒng)的工作原理、硬件組成及軟件實(shí)現(xiàn)。系統(tǒng)采

2009-03-13 11:25:08 20

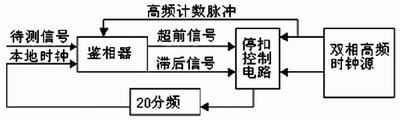

20 介紹了EPA通信協(xié)議模型和EPA通信調(diào)度規(guī)程,根據(jù)通信調(diào)度的原理和要求,研究了EPA協(xié)議確定性調(diào)度的測(cè)試原理,提出了測(cè)試EPA確定性調(diào)度的方法和系統(tǒng)結(jié)構(gòu),對(duì)調(diào)度偏差和調(diào)度順序

2009-03-16 17:42:23 6

6 本文提出了一種使用FPGA 實(shí)現(xiàn)誤碼率測(cè)試的設(shè)計(jì)及實(shí)現(xiàn)方法。該設(shè)計(jì)可通過FPGA 內(nèi)建的異步串行接口向主控計(jì)算機(jī)傳遞誤碼信息,也可以通過數(shù)碼管實(shí)時(shí)顯示一段時(shí)間內(nèi)的誤碼率。文

2009-06-26 17:32:46 55

55 本文介紹了基于測(cè)試儀在Windows 98 下實(shí)現(xiàn)電路板維修測(cè)試儀軟件系統(tǒng)的原理、方法和技術(shù)。我們著重介紹了器件功能表的邏輯編程、測(cè)試邏輯和測(cè)試功能實(shí)現(xiàn)等方面的研究成果。[

2009-08-03 11:40:31 39

39 本文運(yùn)用黑盒測(cè)試的基本理論,提出了FPGA邏輯設(shè)計(jì)的測(cè)試模型,分析了FPGA邏輯設(shè)計(jì)的基本方法和步驟,最后結(jié)合一個(gè)實(shí)際項(xiàng)目說明了FPGA邏輯設(shè)計(jì)的測(cè)試驗(yàn)證過程。關(guān)鍵詞:黑盒

2009-08-19 09:12:41 9

9 本文重點(diǎn)對(duì)衛(wèi)星定位系統(tǒng)的測(cè)距方法進(jìn)行了分析與研究,并從時(shí)域和頻域各提出了一種高精度的測(cè)距方法,然后對(duì)其進(jìn)行了matlab 仿真。通過比較仿真結(jié)果,在FPGA 實(shí)現(xiàn)時(shí)選則了一

2009-08-29 10:37:57 26

26 通過模糊自整定PID 控制器的設(shè)計(jì),本文提出了一種基于VHDL 描述、DSP Builder 和Modelsim 混合仿真、FPGA實(shí)現(xiàn)的智能控制器設(shè)計(jì)及測(cè)試新方法。首先,通過MATLAB 仿真,得出智能控制器的結(jié)

2009-09-04 09:34:11 17

17 測(cè)試系統(tǒng)的特性:1.建立測(cè)試系統(tǒng)的概念2.掌握描述測(cè)試系統(tǒng)靜態(tài)特性的方法3.掌握描述測(cè)試系統(tǒng)動(dòng)態(tài)特性的方法4.掌握實(shí)現(xiàn)系統(tǒng)不失真測(cè)試的條件

3.1 測(cè)試系統(tǒng)與線性系統(tǒng)測(cè)試

2009-11-14 08:21:07 32

32 針對(duì)FPGA 中包含三級(jí)可編程開關(guān)的互連網(wǎng)絡(luò)測(cè)試,該文提出了一種基于匹配理論的減少配置次數(shù)并且與陣列規(guī)模無關(guān)的測(cè)試方法。該方法通過建立結(jié)構(gòu)測(cè)試圖,按照?qǐng)D的道路長(zhǎng)進(jìn)行分

2009-11-17 12:43:40 10

10 摘要:本文通過對(duì)一款系統(tǒng)芯片(System on Chip SoC)——“成電之芯”的功能測(cè)試平臺(tái)的搭建,介紹了一種實(shí)現(xiàn)系統(tǒng)芯片功能測(cè)試的方法。關(guān)鍵詞:系統(tǒng)芯片;雷達(dá)信號(hào)處理電路;

2009-12-21 09:59:44 20

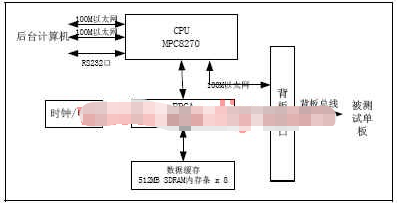

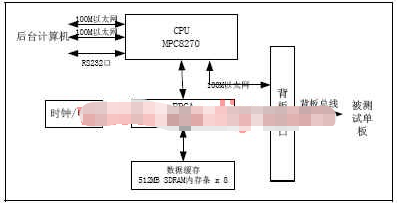

20 本文介紹了基帶測(cè)試系統(tǒng)中,如何應(yīng)用FPGA實(shí)現(xiàn)后臺(tái)計(jì)算機(jī)與測(cè)試環(huán)境數(shù)據(jù)交互以及存儲(chǔ)的電路設(shè)計(jì)流程,并已在某基站測(cè)試系統(tǒng)中成功應(yīng)用。

2010-08-09 15:00:32 27

27 主要內(nèi)容一、為什么需要做自動(dòng)測(cè)試?二、EMI自動(dòng)測(cè)試系統(tǒng)設(shè)計(jì)三、EMS自動(dòng)測(cè)試系統(tǒng)設(shè)計(jì)四、EMC自動(dòng)測(cè)試系統(tǒng)集成實(shí)例五、手機(jī)EMI自動(dòng)測(cè)試實(shí)現(xiàn)

2010-09-21 11:29:23 62

62 設(shè)計(jì)了一種基于FPGA的單板單片主控器件的低成本即插即用虛擬測(cè)試系統(tǒng)。系統(tǒng)包括兩路分立信號(hào)源、一路虛擬存儲(chǔ)示波器和16路高速虛擬邏輯分析儀,結(jié)合FPGA、高速DAC/ADC設(shè)計(jì)特點(diǎn),

2010-12-14 10:07:12 16

16 隨著FPGA設(shè)計(jì)復(fù)雜度的增加,傳統(tǒng)測(cè)試方法受到限制。在高速集成FPGA測(cè)試中,其內(nèi)部信號(hào)的實(shí)時(shí)獲取和分析比較困難。介紹了Quartus II中SingalTap II嵌入式邏輯分析器的使用,并給出一個(gè)

2010-12-17 15:25:17 16

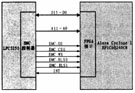

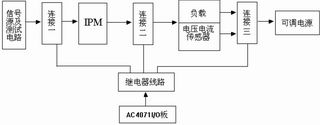

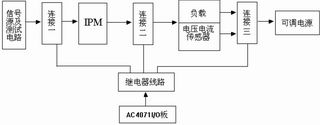

16 摘 要: IPM測(cè)試需要測(cè)試多個(gè)參數(shù),這些不同的參數(shù)需要不同的測(cè)試平臺(tái)。本文通過對(duì)各種不同參數(shù)的測(cè)試方法進(jìn)行研究,設(shè)計(jì)并實(shí)現(xiàn)了自動(dòng)測(cè)試平臺(tái)。問題的提出火車

2006-03-11 13:45:29 744

744

本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測(cè)試系統(tǒng)具有較強(qiáng)的競(jìng)爭(zhēng)力。本系統(tǒng)在FPGA單板

2009-02-12 11:49:27 418

418

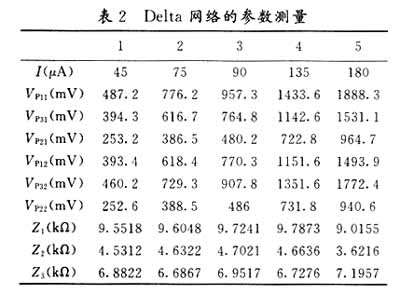

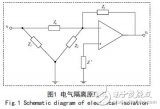

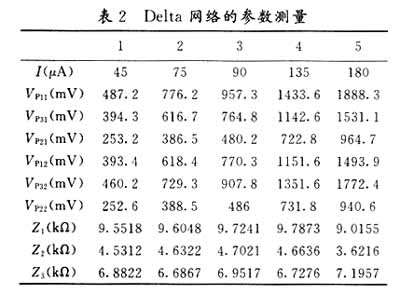

基于IEEE1149.4的測(cè)試方法研究

根據(jù)混合信號(hào)邊界掃描測(cè)試的工作機(jī)制,提出了符合1149.4標(biāo)準(zhǔn)的測(cè)試方法,并用本研究室開發(fā)的混合信號(hào)邊界掃描測(cè)試系統(tǒng)進(jìn)行了測(cè)試

2009-05-04 22:29:18 1007

1007

根據(jù)混合信號(hào)邊界掃描測(cè)試的工作機(jī)制,提出了符合1149.4標(biāo)準(zhǔn)的測(cè)試方法,并用本研究室開發(fā)的混合信號(hào)邊界掃描測(cè)試系統(tǒng)進(jìn)行了測(cè)試驗(yàn)證。

2009-05-09 11:42:12 578

578 FPGA 重復(fù)配置和測(cè)試的實(shí)現(xiàn)

從制造的角度來講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括

2009-09-03 11:17:08 528

528

基于FPGA的PCB測(cè)試機(jī)硬件電路設(shè)計(jì)研究

引言

PCB 光板測(cè)試機(jī)基本的測(cè)試原理是歐姆定律,其測(cè)試方法是將待測(cè)試點(diǎn)間加一定的測(cè)試電壓,用譯碼電路選中PCB

2010-01-04 09:12:33 957

957

FPGA重復(fù)配置和測(cè)試的實(shí)現(xiàn)

從制造的角度來講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA

2010-01-26 09:39:56 544

544

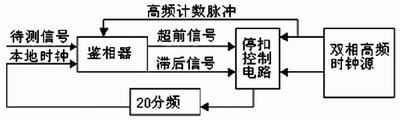

基于FPGA的新型誤碼測(cè)試儀的設(shè)計(jì)與實(shí)現(xiàn)

本文設(shè)計(jì)實(shí)現(xiàn)了一種用于測(cè)量基帶傳輸信道的誤碼儀,闡述了主要模塊的工作原理,提出了一種新的積分鑒相同步時(shí)鐘提取的實(shí)

2010-02-09 10:42:01 876

876

基站發(fā)射系統(tǒng)匹配測(cè)試方法研究

基站發(fā)射系統(tǒng)是移動(dòng)通信系統(tǒng)的重要組成部分,其性能優(yōu)劣對(duì)整體移動(dòng)通信質(zhì)量的影響至關(guān)重要。根據(jù)移動(dòng)網(wǎng)運(yùn)行質(zhì)量統(tǒng)計(jì)結(jié)果分析,

2010-01-06 14:18:29 850

850 現(xiàn)代科技對(duì)系統(tǒng)的可靠性提出了更高的要求,而FPGA技術(shù)在電子系統(tǒng)中應(yīng)用已經(jīng)非常廣泛,因此FPGA易測(cè)試性就變得很重要。要獲得的FPGA內(nèi)部信號(hào)十分有限、FPGA封裝和印刷電路板(PCB)

2010-08-04 17:35:45 600

600

本文提出了一種基于SoPC的FPGA在線測(cè)試方法,是對(duì)現(xiàn)有FPGA在線測(cè)試方法的一種有效的補(bǔ)充。

2011-04-18 11:46:20 1145

1145

誤碼測(cè)試儀是檢測(cè)通信系統(tǒng)可靠性的重要設(shè)備。傳統(tǒng)的誤碼測(cè)試儀基于CPLD和CPU協(xié)同工作,不僅結(jié)構(gòu)復(fù)雜,價(jià)格昂貴,而且不方便攜帶。基于FPGA的高速誤碼測(cè)試儀,采用FPGA來完成控制和

2011-05-06 16:03:07 42

42 本文就調(diào)試FPGA系統(tǒng)時(shí)遇到的問題及有助于提高調(diào)試效率的方法,針對(duì)Altera和Xilinx的FPGA調(diào)試提供了最新的方法和工具。

2011-09-27 14:28:39 750

750

基于對(duì)FPGA系統(tǒng)失效機(jī)理的深入分析, 提出了軟件測(cè)試技術(shù)在FPGA測(cè)試中的應(yīng)用, 并分析了其可行性; 通過對(duì)比FPGA與軟件系統(tǒng)的異同, 歸納出FPGA特有的測(cè)試要求,從而在軟件測(cè)試技術(shù)的基礎(chǔ)

2011-09-29 17:41:21 65

65 誤碼儀是評(píng)估信道性能的基本測(cè)量?jī)x器。本文介紹的誤碼儀結(jié)合FPGA 的特點(diǎn),采用全新的積分式鑒相結(jié)構(gòu),提出了一種新的誤碼測(cè)試方法,經(jīng)多次測(cè)試驗(yàn)證,方案可行,設(shè)計(jì)的系統(tǒng)穩(wěn)定。

2012-05-02 14:31:02 808

808

本文核心提示: 隨著FPGA接口的速度提高,高速接口的測(cè)試、PCB板級(jí)的測(cè)試、EMI/EMC的測(cè)試等,這些測(cè)試的難度會(huì)越來越突出。想要實(shí)現(xiàn)FPGA的自動(dòng)化測(cè)試的話,就需要提高軟件的可控性和

2012-08-27 10:09:08 972

972 基于FPGA的ADC指標(biāo)測(cè)量及測(cè)試系統(tǒng)。

2016-05-10 11:47:13 13

13 基于反熔絲的FPGA的測(cè)試方法_馬金龍

2017-01-07 19:08:43 2

2 汽車ECU測(cè)試系統(tǒng)的研究與實(shí)現(xiàn)_莫太平

2017-01-19 21:54:15 14

14 基于LabVIEW與FPGA的飛行訓(xùn)練彈測(cè)試系統(tǒng)設(shè)計(jì)_劉克軒

2017-02-07 18:22:06 6

6 IT硬件能耗測(cè)試方法應(yīng)用研究_黃植勤

2017-03-19 11:27:34 2

2 STUN協(xié)議的實(shí)現(xiàn)原理及測(cè)試方法研究_吳任國(guó)

2017-03-19 11:28:02 0

0 基于FPGA和無線通信的密立根油滴測(cè)試系統(tǒng)設(shè)計(jì)_徐富新

2017-03-19 19:08:35 0

0 了基于magnumII測(cè)試系統(tǒng)的測(cè)試技術(shù)研究,提出了采用magnumII測(cè)試系統(tǒng)的APG及其他模塊實(shí)現(xiàn)對(duì)MRAMVDMR8M32進(jìn)行電性測(cè)試及功能測(cè)試。

2017-09-19 08:49:26 24

24 基于DSP的FPGA配置方法研究與實(shí)現(xiàn)

2017-10-19 16:15:19 36

36 隨著FPGA在現(xiàn)代電子系統(tǒng)中應(yīng)用的不斷增多.FPGA的測(cè)試技術(shù)也得到非常快的發(fā)展。其中,內(nèi)建白測(cè)試(BIST)的方法已經(jīng)成為一種主流的解決方案。BIST方法一般來說可以分為兩大類,一類是離線BIST

2017-11-08 14:21:46 1

1 ,不利于硬件的開發(fā)進(jìn)度。面對(duì)這一難題,文章從FPGA 的軟硬件協(xié)同測(cè)試角度出發(fā),利用PC 機(jī)和測(cè)試硬件設(shè)備的特點(diǎn),進(jìn)行FPGA 的軟硬件協(xié)同測(cè)試的設(shè)計(jì),努力實(shí)現(xiàn)FPGA 的軟硬件協(xié)調(diào)測(cè)試系統(tǒng)在軟硬件的測(cè)試和分析中的應(yīng)用。

2017-11-18 05:46:28 1616

1616 FPGA 具有高速度、高集成度,可重復(fù)編程的特點(diǎn),將其用于電路系統(tǒng)設(shè)計(jì),可簡(jiǎn)化電路設(shè)計(jì),增強(qiáng)電路功能。而作為電路系統(tǒng)的“中樞控制神經(jīng)”,FPGA 的故障會(huì)引起整個(gè)電路系統(tǒng)的癱瘓,而用一般的測(cè)試方法很難對(duì)其實(shí)施故障測(cè)試診斷。

2018-07-18 14:37:00 1088

1088

從制造的角度來講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA、然后是測(cè)試FPGA,配置FPGA是指將FPGA通過

2017-11-24 20:55:53 5922

5922

針對(duì)性地介紹了幾種常用的單片機(jī)系統(tǒng)RAM測(cè)試方法,并在其基礎(chǔ)上提出了一種基于種子和逐位倒轉(zhuǎn)的RAM故障測(cè)試方法。 1 RAM測(cè)試方法回顧 (1)方法1 參考文獻(xiàn)中給出了一種測(cè)試系統(tǒng)RAM的方法。該方法是分兩步來檢查,先后向整個(gè)數(shù)據(jù)區(qū)

2017-12-02 09:07:57 544

544 摘要: 基于對(duì)FPGA系統(tǒng)失效機(jī)理的深入分析,提出了軟件測(cè)試技術(shù)在FPGA測(cè)試中的應(yīng)用,并分析了其可行性;通過對(duì)比FPGA與軟件系統(tǒng)的異同,歸納出FPGA特有的測(cè)試要求,從而在軟件測(cè)試技術(shù)的基礎(chǔ)上

2018-01-19 22:34:59 937

937 儲(chǔ)能系統(tǒng)在可再生能源應(yīng)用中具有多種功能,研究模塊化儲(chǔ)能系統(tǒng)在大規(guī)模可再生能源各種應(yīng)用中的適用性是當(dāng)前研究的熱點(diǎn)之一。文中構(gòu)建并分析了模塊化儲(chǔ)能系統(tǒng)工況測(cè)試曲線。通過因子分析對(duì)儲(chǔ)能系統(tǒng)跟蹤計(jì)劃

2018-01-22 16:27:33 16

16 本文主要講述了web應(yīng)用系統(tǒng)的搭建測(cè)試環(huán)境和web測(cè)試方法,在測(cè)試過程中,有的僅需要手動(dòng)測(cè)試的,有的需要自動(dòng)化測(cè)試工具的幫助,所以web系統(tǒng)的測(cè)試要求測(cè)試人員有很深的自動(dòng)化測(cè)試技術(shù)。

2018-01-31 17:07:33 17914

17914 FPGA可以通過專享的硬件資源進(jìn)行處理數(shù)據(jù),從而實(shí)現(xiàn)較高的吞吐率,可以比通過I/O硬件先獲取數(shù)據(jù)再通過軟件執(zhí)行數(shù)據(jù)處理的速率更快。結(jié)合FPGA技術(shù)的測(cè)試系統(tǒng),不是按照傳統(tǒng)意義上的“采集、數(shù)據(jù)傳輸

2018-10-07 11:47:47 5023

5023 基于FPGA的PCB測(cè)試機(jī)的硬件控制系統(tǒng),提高了PCB測(cè)試機(jī)的測(cè)試速度、簡(jiǎn)化電路的設(shè)計(jì)。

2020-04-01 17:56:56 1688

1688 基于FPGA的PCB測(cè)試機(jī)的硬件控制系統(tǒng),提高了PCB測(cè)試機(jī)的測(cè)試速度、簡(jiǎn)化電路的設(shè)計(jì)。

2019-10-23 15:15:45 1867

1867 在基站的模擬測(cè)試系統(tǒng)中,終端控制子系統(tǒng)負(fù)責(zé)生成上行測(cè)試數(shù)據(jù)并將其發(fā)送到被測(cè)基帶板,測(cè)試基帶板上行接收的功能及性能;同時(shí)根據(jù)后臺(tái)控制采集下行發(fā)射的基帶數(shù)據(jù)并送后臺(tái)進(jìn)行分析,測(cè)試其發(fā)射功能。而FPGA部分屬于終端控制子系統(tǒng)的前臺(tái)部分,負(fù)責(zé)IQ數(shù)據(jù)的發(fā)送及采集,基帶測(cè)試板的功能主要在這里面實(shí)現(xiàn)。

2020-08-07 17:53:52 892

892

本文著重分析晶閘管直流參數(shù)的測(cè)試方法,并實(shí)現(xiàn)其自動(dòng)化測(cè)試。本文首先

詳細(xì)分析了晶閘管的各個(gè)直流參數(shù)的測(cè)量方法,并給出了各個(gè)參數(shù)相應(yīng)的測(cè)試電

路原理圖。其次,本文介紹了測(cè)試平臺(tái)的硬件總體構(gòu)成和軟件

2022-07-05 17:49:24 2

2 作者|J小編|吃不飽模糊測(cè)試是網(wǎng)絡(luò)安全測(cè)試領(lǐng)域必然會(huì)被提及的一類測(cè)試方法。它有著極其鮮明的特點(diǎn),包括極低的需求依賴性、可逆向的測(cè)試理念等,與常規(guī)測(cè)試方法顯得是那么的“風(fēng)格迥異”。但同時(shí),這種測(cè)試方法

2022-09-15 11:09:06 354

354

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 大容量、高速率和低功耗已成為FPGA的發(fā)展重點(diǎn)。 嵌入式邏輯分析工具無法滿足通用性要求,外部測(cè)試工具可以把FPGA內(nèi)部信號(hào)與實(shí)際電路聯(lián)合起來觀察系統(tǒng)真實(shí)運(yùn)行情況。 隨著

2023-10-23 15:20:01 460

460

電子發(fā)燒友網(wǎng)站提供《基于ARM9平臺(tái)和FPGA的1553B總線測(cè)試系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-11-08 10:10:29 0

0

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論